- 当前位置:首页 >隴南市 >消息稱三星背麵供電芯片測試結果良好 有望提前導入

消息稱三星背麵供電芯片測試結果良好 有望提前導入

发布时间:2025-11-02 11:14:36 来源:水中捉月網 作者:地方

-

2 月 29 日消息,據韓媒 Chosunbiz 報道,三星電子近日在背麵供電網絡(BSPDN)芯片測試中獲得了好於預期的成果,有望提前導入未來製程節點。

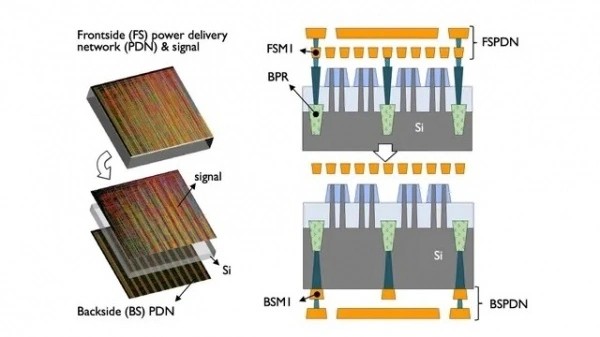

傳統芯片采用自下而上的製造方式,先製造晶體管再建立用於互連和供電的線路層。但隨著製程工藝的收縮,傳統供電模式的線路層越來越混亂,對設計與製造形成幹擾。

BSPDN 技術將芯片供電網絡轉移至晶圓背麵,可簡化供電路徑,解決互連瓶頸,減少供電對信號的幹擾,最終可降低平台整體電壓與功耗。對於三星而言,還特別有助於移動端 SoC 的小型化。

▲ BSPDN 背麵供電網絡示意圖。圖源 imec

參考韓媒報道,三星電子在測試晶圓上對兩種不同的 ARM 內核設計進行了測試,在芯片麵積上分別減小了 10% 和 19%,同時還獲得了不超過 10% 的性能、頻率效率提升。

Chosunbiz 稱,三星此前考慮在 2027 年左右的 1.7nm(IT之家注:此處存疑,以往報道中為 1.4nm)工藝中實現背麵供電技術的商業化,但由於目前超額完成了開發目標,預計將修改路線圖,最早在明年推出的 2nm 中應用。

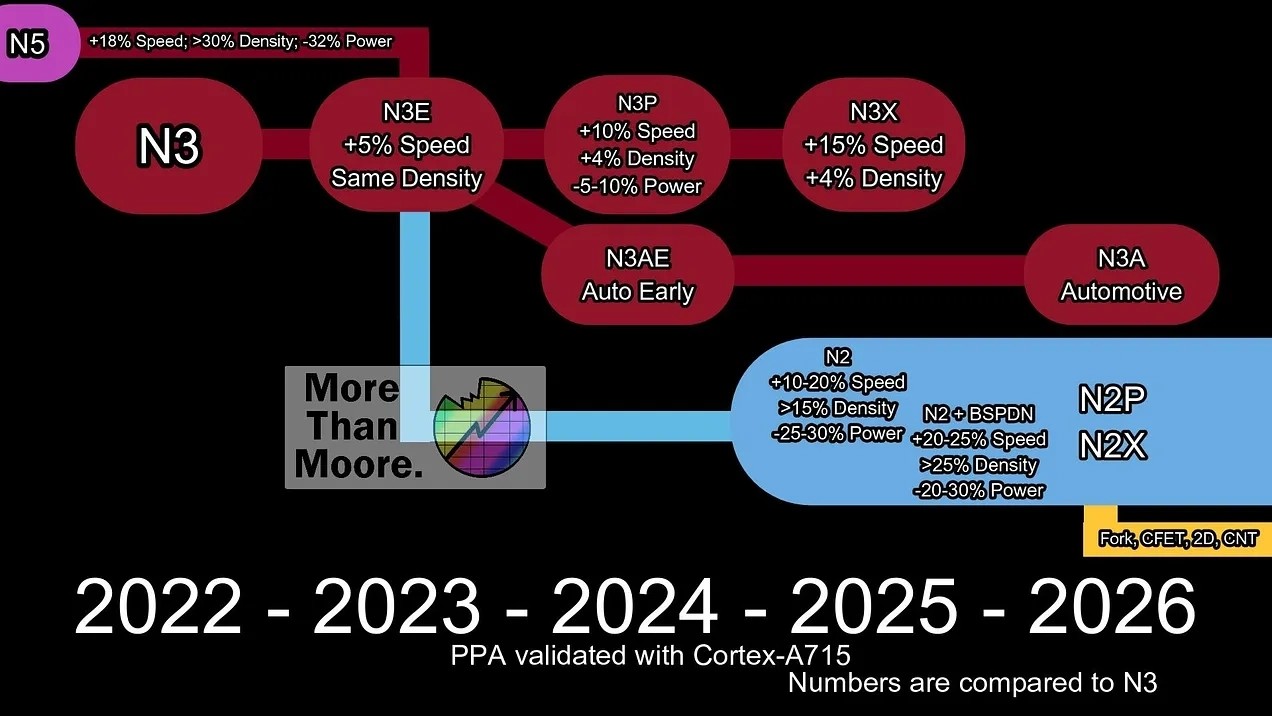

三星電子的兩大競爭對手台積電和英特爾也積極布局背麵供電領域:其中英特爾將於今年的 20A 節點開始推出其 BSPDN 實現 PowerVia;而根據科技博客 More Than Moore 消息,台積電預計將在 2025 年推出標準 N2 節點後 6 個月左右發布對應的背麵供電版本。

▲ 台積電未來技術路線圖。圖源科技博客 More Than Moore

- https://hkstudyroute.com/five-things-to-do-in-college/

- https://hkstudyroute.com/the-salary-of-a-mortician/

- https://hkstudyroute.com/high-school-knock-success-rate/

- https://hkstudyroute.com/tennis-course/

- https://hkstudyroute.com/lactation-consultant/

- https://hkstudyroute.com/library-data-organizer/

- https://hkstudyroute.com/feng-shui-masters-charges/

- https://hkstudyroute.com/kindergarten-interview-questions/

- https://hkstudyroute.com/lawyers-letter-fee/

- https://hkstudyroute.com/saturation-of-speech-therapists/

相关文章

2021年销量榜验成色:想要征战全球市场的中国车企有哪九家?欧司朗高品质解决方案工业领域专区2022年天然气行业研究报告新能源汽车地方补贴:又来一波!预防近视从“光源”开始!旺泓LED防蓝光灯珠新能源汽车地方补贴:又来一波!第二、三曲线成型,百度穿越增长周期?促销费政策组合拳发布 车市增量有望超百万国轩高科发布360Wh/kg半固态电池,进入产业化阶段营收缩水 255 亿元后,昔日苹果供应链巨头瞄准元宇宙(VR/AR)https://hkstudyroute.com/aircraft-maintenance-apprentice/https://hkstudyroute.com/ranking-of-kwai-tsing-secondary-schools/https://hkstudyroute.com/free-psychology-course/https://hkstudyroute.com/self-study-korean/https://hkstudyroute.com/group-discussion-skills/https://hkstudyroute.com/hello-world/https://hkstudyroute.com/international-school-for-the-common-people/https://hkstudyroute.com/middle-school-entrance-interview-class/https://hkstudyroute.com/introduce-yourself-at-the-interview/

- Copyright © 2016 Powered by 消息稱三星背麵供電芯片測試結果良好 有望提前導入,水中捉月網 sitemap